硅晶MEMS 0scillator頻率公差與可靠性

來(lái)源:http://m.netflixyz.com 作者:金洛鑫電子 2019年07月17

長(zhǎng)期以來(lái),晶體振蕩器已與模擬振蕩器保持電路結(jié)合使用,該電路驅(qū)動(dòng)0scillator以特定頻率振動(dòng).今天,硅MEMS換能器是另一種選擇,這些器件在嘈雜的環(huán)境中勝過(guò)石英晶體.隨著通信速度的提高和移動(dòng)通信的普及,對(duì)雞群來(lái)源的需求日益嚴(yán)峻.此外,無(wú)論電子設(shè)備是復(fù)雜還是時(shí)鐘頻率很高,時(shí)鐘設(shè)備必須在嘈雜的環(huán)境中繼續(xù)良好運(yùn)行.

本文介紹了使用石英振蕩器和硅MEMS振蕩器進(jìn)行的對(duì)比實(shí)驗(yàn)的結(jié)果.從這些數(shù)據(jù)可以確定,MEMS振蕩器在真實(shí)的環(huán)境條件下優(yōu)于石英振蕩器.振蕩器制造商為每種產(chǎn)品提供數(shù)據(jù)表,其中包括頻率穩(wěn)定性,抖動(dòng)和相位噪聲等性能參數(shù).雖然數(shù)據(jù)表是選擇計(jì)時(shí)設(shè)備時(shí)的一個(gè)很好的指標(biāo),但用戶應(yīng)評(píng)估這些設(shè)備在實(shí)際環(huán)境條件下的工作方式.

在模擬實(shí)際操作環(huán)境的條件下進(jìn)行測(cè)試可以提供有關(guān)準(zhǔn)確組件性能的有價(jià)值信息.與理想條件下的振蕩器相比,受到環(huán)境壓力因素(如電磁干擾(EMI),振動(dòng),電源或其他系統(tǒng)組件噪聲)的振蕩器性能下降.在最壞的情況下,環(huán)境壓力因素會(huì)降低設(shè)備可靠性或縮短設(shè)備壽命.選擇定時(shí)器件時(shí),在實(shí)際和惡劣的噪聲條件下考慮振蕩器性能非常重要.

硅MEMS的優(yōu)點(diǎn)

SiTime可編程振蕩器與石英諧振器相比具有幾個(gè)固有的優(yōu)點(diǎn),以確保它們?cè)诓煌h(huán)境中工作的能力.SiTime開(kāi)發(fā)了一種MEM SFirstTM工藝,可在位于硅芯片中的微型真空容器[1]中創(chuàng)建并密封傳感器.微小質(zhì)量振動(dòng)器與其硬質(zhì)硅晶體結(jié)構(gòu)的組合提高了耐久性,并且對(duì)諸如沖擊和振動(dòng)的外部應(yīng)力的抵抗力變得非常強(qiáng).是的.此外,構(gòu)成振蕩器的最佳設(shè)計(jì)模擬電路在電噪聲條件下表現(xiàn)良好.

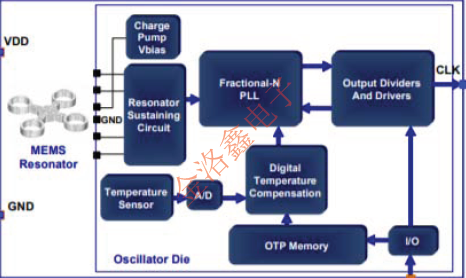

圖1中的MEMS振蕩器結(jié)構(gòu)示意圖顯示了由精確調(diào)節(jié)的硅MEMS振蕩器,振蕩保持電路,高精度N分頻鎖相環(huán)(PLL)和全差分電路組成的輸出.它顯示了有助于提高性能和可靠性的重要部件,例如驅(qū)動(dòng)電路. 大部分晶振廠家都是專門(mén)從事振蕩器制造的,但不一定是電路設(shè)計(jì)的專家.他們把使用的模擬電路委托給外部,所以不能說(shuō)是針對(duì)特定的振子進(jìn)行了優(yōu)化,反而不得不購(gòu)買(mǎi)被設(shè)計(jì)為在各種水晶上工作的芯片.相比之下,sitime擁有模擬設(shè)計(jì)者的專業(yè)團(tuán)隊(duì),該團(tuán)隊(duì)設(shè)計(jì)了與sitime的MEMS振蕩器一起使用的所有電路.自2006年以來(lái),該團(tuán)隊(duì)在sitime的振蕩器產(chǎn)品的性能和耐久性上有了戲劇性的提高,其結(jié)果是,在噪聲環(huán)境條件下,sitime的MEMS振蕩器比晶體器件具有更強(qiáng)的耐久性.

運(yùn)行環(huán)境壓力因素

操作環(huán)境中的幾個(gè)因素會(huì)降低相位噪聲和抖動(dòng),這會(huì)對(duì)振蕩器性能產(chǎn)生不利影響.本書(shū)依次分析了環(huán)境條件對(duì)SiTime和競(jìng)爭(zhēng)廠商制造的振蕩器性能的影響.

電源噪聲

任何系統(tǒng)中的主要噪聲源之一是電源.大多數(shù)噪聲被放置在貼片振蕩器電源輸入端的無(wú)源濾波器和去耦電容器拒絕.但是,無(wú)法消除的剩余噪聲會(huì)增加輸出時(shí)鐘的抖動(dòng),并可能對(duì)系統(tǒng)中的時(shí)序裕度產(chǎn)生不利影響.這種噪聲不僅在通電時(shí)放大,而且在系統(tǒng)運(yùn)行期間電路板上的其他設(shè)備打開(kāi)或關(guān)閉時(shí)也會(huì)放大.電源濾波和接地反彈等基板問(wèn)題也會(huì)影響噪聲和抖動(dòng).

PSRR(電源抑制比)是模擬電路設(shè)計(jì)中使用的參數(shù),用作指示電路對(duì)電源噪聲的容差的特定參數(shù).與以dB表示的SNR相關(guān)參數(shù)PSRR不同,噪聲功率條件下的振蕩器性能以電源噪聲靈敏度(PSNS)表示.PSNS通過(guò)振蕩器在20kHz至20MHz的指定頻率范圍內(nèi)應(yīng)用峰峰值噪聲時(shí)表現(xiàn)出的相位抖動(dòng)進(jìn)行量化.

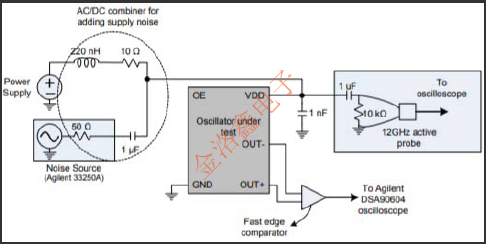

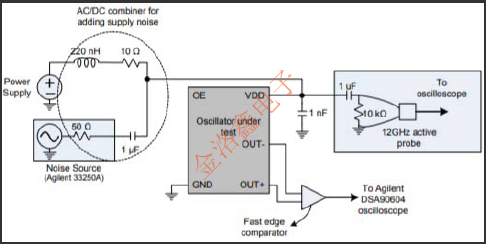

圖2.電源噪聲抑制測(cè)試設(shè)置的框圖

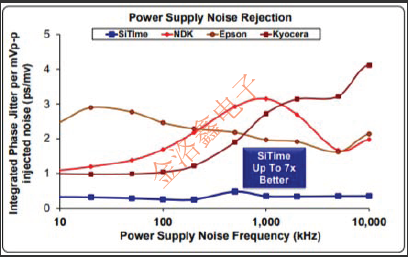

圖2所示的以電源及波形發(fā)生器為首的測(cè)試設(shè)置是用于評(píng)價(jià)晶振的psns性能的測(cè)試方法.波形發(fā)生器為了測(cè)量電源噪聲對(duì)振蕩器抖動(dòng)的影響,在測(cè)量條件的電壓和頻率上加上系統(tǒng)噪聲.圖3的曲線表示在50mv峰值to峰值處提供開(kāi)關(guān)電源噪聲時(shí)的相位抖動(dòng)狀態(tài),對(duì)于LVCmos輸出用的sitimeMEMS振蕩器,比較了各種晶體振蕩器的比較結(jié)果.

如圖表所示,在所有噪聲頻率下,靜態(tài)MEMS振蕩器的抖動(dòng)都是最低的.其理由是,sitime的振蕩器電路中裝入了保護(hù)振蕩器不受電源引起的抖動(dòng)影響的降噪電路.

本文介紹了使用石英振蕩器和硅MEMS振蕩器進(jìn)行的對(duì)比實(shí)驗(yàn)的結(jié)果.從這些數(shù)據(jù)可以確定,MEMS振蕩器在真實(shí)的環(huán)境條件下優(yōu)于石英振蕩器.振蕩器制造商為每種產(chǎn)品提供數(shù)據(jù)表,其中包括頻率穩(wěn)定性,抖動(dòng)和相位噪聲等性能參數(shù).雖然數(shù)據(jù)表是選擇計(jì)時(shí)設(shè)備時(shí)的一個(gè)很好的指標(biāo),但用戶應(yīng)評(píng)估這些設(shè)備在實(shí)際環(huán)境條件下的工作方式.

在模擬實(shí)際操作環(huán)境的條件下進(jìn)行測(cè)試可以提供有關(guān)準(zhǔn)確組件性能的有價(jià)值信息.與理想條件下的振蕩器相比,受到環(huán)境壓力因素(如電磁干擾(EMI),振動(dòng),電源或其他系統(tǒng)組件噪聲)的振蕩器性能下降.在最壞的情況下,環(huán)境壓力因素會(huì)降低設(shè)備可靠性或縮短設(shè)備壽命.選擇定時(shí)器件時(shí),在實(shí)際和惡劣的噪聲條件下考慮振蕩器性能非常重要.

硅MEMS的優(yōu)點(diǎn)

SiTime可編程振蕩器與石英諧振器相比具有幾個(gè)固有的優(yōu)點(diǎn),以確保它們?cè)诓煌h(huán)境中工作的能力.SiTime開(kāi)發(fā)了一種MEM SFirstTM工藝,可在位于硅芯片中的微型真空容器[1]中創(chuàng)建并密封傳感器.微小質(zhì)量振動(dòng)器與其硬質(zhì)硅晶體結(jié)構(gòu)的組合提高了耐久性,并且對(duì)諸如沖擊和振動(dòng)的外部應(yīng)力的抵抗力變得非常強(qiáng).是的.此外,構(gòu)成振蕩器的最佳設(shè)計(jì)模擬電路在電噪聲條件下表現(xiàn)良好.

圖1中的MEMS振蕩器結(jié)構(gòu)示意圖顯示了由精確調(diào)節(jié)的硅MEMS振蕩器,振蕩保持電路,高精度N分頻鎖相環(huán)(PLL)和全差分電路組成的輸出.它顯示了有助于提高性能和可靠性的重要部件,例如驅(qū)動(dòng)電路. 大部分晶振廠家都是專門(mén)從事振蕩器制造的,但不一定是電路設(shè)計(jì)的專家.他們把使用的模擬電路委托給外部,所以不能說(shuō)是針對(duì)特定的振子進(jìn)行了優(yōu)化,反而不得不購(gòu)買(mǎi)被設(shè)計(jì)為在各種水晶上工作的芯片.相比之下,sitime擁有模擬設(shè)計(jì)者的專業(yè)團(tuán)隊(duì),該團(tuán)隊(duì)設(shè)計(jì)了與sitime的MEMS振蕩器一起使用的所有電路.自2006年以來(lái),該團(tuán)隊(duì)在sitime的振蕩器產(chǎn)品的性能和耐久性上有了戲劇性的提高,其結(jié)果是,在噪聲環(huán)境條件下,sitime的MEMS振蕩器比晶體器件具有更強(qiáng)的耐久性.

運(yùn)行環(huán)境壓力因素

操作環(huán)境中的幾個(gè)因素會(huì)降低相位噪聲和抖動(dòng),這會(huì)對(duì)振蕩器性能產(chǎn)生不利影響.本書(shū)依次分析了環(huán)境條件對(duì)SiTime和競(jìng)爭(zhēng)廠商制造的振蕩器性能的影響.

電源噪聲

任何系統(tǒng)中的主要噪聲源之一是電源.大多數(shù)噪聲被放置在貼片振蕩器電源輸入端的無(wú)源濾波器和去耦電容器拒絕.但是,無(wú)法消除的剩余噪聲會(huì)增加輸出時(shí)鐘的抖動(dòng),并可能對(duì)系統(tǒng)中的時(shí)序裕度產(chǎn)生不利影響.這種噪聲不僅在通電時(shí)放大,而且在系統(tǒng)運(yùn)行期間電路板上的其他設(shè)備打開(kāi)或關(guān)閉時(shí)也會(huì)放大.電源濾波和接地反彈等基板問(wèn)題也會(huì)影響噪聲和抖動(dòng).

PSRR(電源抑制比)是模擬電路設(shè)計(jì)中使用的參數(shù),用作指示電路對(duì)電源噪聲的容差的特定參數(shù).與以dB表示的SNR相關(guān)參數(shù)PSRR不同,噪聲功率條件下的振蕩器性能以電源噪聲靈敏度(PSNS)表示.PSNS通過(guò)振蕩器在20kHz至20MHz的指定頻率范圍內(nèi)應(yīng)用峰峰值噪聲時(shí)表現(xiàn)出的相位抖動(dòng)進(jìn)行量化.

圖2.電源噪聲抑制測(cè)試設(shè)置的框圖

如圖表所示,在所有噪聲頻率下,靜態(tài)MEMS振蕩器的抖動(dòng)都是最低的.其理由是,sitime的振蕩器電路中裝入了保護(hù)振蕩器不受電源引起的抖動(dòng)影響的降噪電路.

圖3.SiTime MEMS和Epson SAW振蕩器存在50mV電源噪聲時(shí)的相位抖動(dòng),作為電源開(kāi)關(guān)噪聲頻率的函數(shù)

正在載入評(píng)論數(shù)據(jù)...

相關(guān)資訊

- [2024-03-08]IQD晶體尺寸縮小的設(shè)計(jì)效果LFXT...

- [2024-03-07]Golledge衛(wèi)星通信中的頻率控制產(chǎn)...

- [2024-03-07]Golledge工業(yè)自動(dòng)化和控制系統(tǒng)中...

- [2024-03-06]MTI-milliren恒溫晶振222系列振...

- [2024-03-06]MTI-milliren低G靈敏度銫原子鐘...

- [2024-03-05]GEYER高穩(wěn)定性KXO-V93T低功耗32...

- [2024-03-02]NEL為系統(tǒng)關(guān)鍵應(yīng)用程序設(shè)計(jì)和制...

- [2024-01-06]溫補(bǔ)補(bǔ)償振蕩器的原理及特點(diǎn)

業(yè)務(wù)經(jīng)理

業(yè)務(wù)經(jīng)理 客服經(jīng)理

客服經(jīng)理